# AREA EFFICIENT AND FAULT TOLERANT FIR FILTER

Brajesh Kumar Gupta (nit jamshedpur)

Associate prof. R. Sinha (nit jamshedpur)

Abstract— Triple Modular Redundancy (TMR) and Hamming Codes have been used to protect different circuits against Single Event Upsets (SEUs). In this paper, the use of a Novel Hamming approach on FIR Filters is studied and implemented in order to provide low complexity, reduce delay and area efficient protection techniques for higher bits data.

Index Terms— Single Event Upset (SEU), Hamming codes, Novel Hamming codes, Reliability, Digital filters, FPGA, Xilinx 9.2

## 1. INTRODUCTION

Memory cells have been protected from soft errors for more than a decade; due to the increase in soft error rate in logic circuits, the encoder and decoder circuitry around the memory blocks have become susceptible to soft errors as well and must also be protected

Figure 1 : Energetic particles causing SEEs

In some environments, such as space, radiation sources are abundant as is evident in figure 1. The effects of radiations are a well-known cause of errors in microelectronic circuits [1]. These errors range from temporary failures of the system (which most of the times produce a restart of the operations) to serious and permanent damage of the devices. One type of temporary effects is Single Event Effects (SEEs), that cause undesirable changes in the values of flips -flops (SEUs) or combinational logic (SETs) [2]. When a particle hits the silicon, it loses its energy and transmits it to the silicon, causing a current burst. In the case of SEUs, these can randomly change the content of storage cells. To protect storage cells of integrated circuits from this phenomenon, several approaches may be followed[3][4]. One is by technology hardening of memory cells and another one is by designing circuits able to detect an SEU event and act accordingly to prevent error propagation and guarantee full reliability in the system. Triple Modular Redundancy (TMR) and Error Detection and Correction Code (EDAC), like Hamming Code, are examples of such methods.

Filters are commonly used in digital communication systems for equalization, signal separation, noise reduction, etc. As communications are fundamental for space borne applications, such as satellites, unmanned missions, etc., digital filters play an important role in space systems [5].

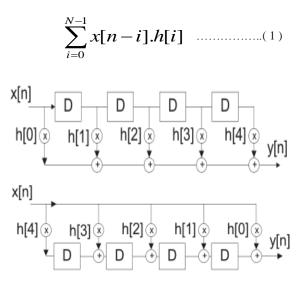

This paper introduces optimizations for the use of improved Hamming Codes to protect generic (FIR) filter, described by (1) and illustrated in Figure 2. It shows that by knowing attributes of the design to protect the circuit, it is possible to reduce resource consumption and achieve an optimal design.

Figure 2 : Direct Form FIR filter structure and transposed FIR Filter structure.

HAMMING code is well known for its single-bit error detection and correction capability. Hamming code is based on the principle of adding 'r' redundancy bits to 'n' data bits such that

$2^r \ge n + r + 1$

IJSER © 2013 http://www.ijser.org For example, it needs 4 redundancy bits for a 7-bit data item and 6 redundancy bits for a 56-bit data stream. Let us say, the 7-bit data to be transmitted is 0111001. Then the 11-bit data actually transmitted is 011P100P1PP, where the P's refer to the Hamming bits that are to be calculated and interspersed at bit positions 1, 2, 4, & 8. Thus the 11-bit data actually transmitted is 01101001111. For the calculation of Hamming bits at positions 1, 2, 4, & 8, even-parity checks were performed on 6, 6, 4, & 4 bits respectively. Thus a total of 20 bits are involved in the process of Hamming bits calculations. The error-detection and correction process in Hamming code is as illustrated in Table 1 Hamming code is normally used for transmission of 7-bit data item. Scaling it for larger data lengths results in a lot of overhead due to interspersing the redundancy bits and their removal later, it is not efficient for higher data bit

### 2. PROPOSED NOVEL HAMMING CODE

A novel Hamming code is proposed in this section , to increase the efficiency of higher data bits. Let us consider the same example. The 7-bit data to be transmitted is 0111001. The number of redundancy bits, 'r' to be appended to n-bit data is obtained such that the relation

$$(2^{r-1}-1) \ge n$$

is satisfied. The number of redundancy bits in this method is same as that for Hamming code for some values of n. But in some cases, it will be just one more redundancy bit than needed in the Hamming code[6][7][8]. For 7-bit data, the number of redundancy bits required will be 4. Then the 11-bit data actually transmitted is PPPP0111001, where the P's refer to the redundancy bits that are to be calculated and appended at bit positions 8, 9, 10, & 11. Thus the 11-bit data actually transmitted is **0110**0111001. For the calculation of bits at positions 8, 9, 10, & 11, even-parity checks were performed on 5, 5, 5, & 4 bits respectively. Thus a total of 19 bits are involved in the process of calculation of redundancy bits. The errordetection and correction process as proposed in this novel method is illustrated in Table 2.

TABLE1 : ERROR DETECTION AND CORRECTION USING HAMMING CODE

| 1  | Recieved information include Hamming bits |   |   |   |   |   |   |   |   |   |            | s of Pa         | Conclusion |    |                            |

|----|-------------------------------------------|---|---|---|---|---|---|---|---|---|------------|-----------------|------------|----|----------------------------|

| 11 | 10                                        | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | <b>S</b> 3 | <mark>S2</mark> | <b>S</b> 1 | SO |                            |

| 0  | 1                                         | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | Т          | F               | T          | F  | Error at bit<br>position 5 |

| 0  | 1                                         | 1 | 1 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | F          | T               | Т          | Т  | Error at bit position 8    |

| 0  | 1                                         | 1 | 0 | 1 | 0 | 0 | 1 | 1 | 1 | 1 | Т          | T               | Ţ          | т  | No Error                   |

TABLE 2 : ERROR DETECTION AND CORRECTION USING NOVEL METHOD

| Conclusion              | Recieved information including redundancy bits Status of Parity check |           |            |            |   |   |   |   |   |   |   |   |   |    |    |

|-------------------------|-----------------------------------------------------------------------|-----------|------------|------------|---|---|---|---|---|---|---|---|---|----|----|

|                         | SO                                                                    | <b>S1</b> | <b>S</b> 2 | <b>S</b> 3 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 |

| Error at bit position 6 | T                                                                     | F         | F          | Т          | 1 | 0 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1  | 0  |

| Error at bit position 8 | F                                                                     | Т         | Т          | F          | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 | 1 | 1  | 0  |

| Error at bit position 9 | Т                                                                     | F         | Т          | F          | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 0 | 1  | 0  |

| Error at bit position10 | Т                                                                     | Т         | F          | F          | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 0  | 0  |

| Error at bit position11 | Т                                                                     | Т         | F          | Т          | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1  | 1  |

| No Error                | Т                                                                     | T         | F          | Т          | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 0 | 1 | 1  | 0  |

TABLE 3 : COMPARISON OF NUMBER OF BITS INVOLVED IN CALCULATION OF REDUNDANCY BITS

| Length of data stream | Number of bits involved in calculation of Redundancy bits in <b>Hamming code</b> | Number of bits involved in calculation of Redundancy bits in <b>Novel Hamming code</b> |

|-----------------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 7 bit data            | 20 bits involved                                                                 | 19 bits involved                                                                       |

| 31 bit data           | 93 bits involved                                                                 | 90 bits involved                                                                       |

| 56 bit data           | 182 bits involved                                                                | 172 bits involved                                                                      |

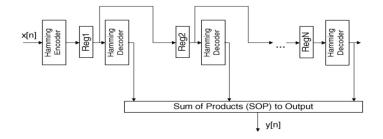

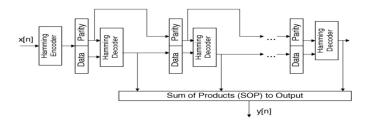

TMR is the simplest and effective way for protecting a design. The area consumption of this method is obviously up to three times higher, depending on which implementation is chosen. The optimal design of the TMR logic is discussed in [9]. A previous approach to protect FIR filters using Hamming codes as discussed in [10] is illustrated in Fig. 3 and Fig. 4. EDAC codes to protect the circuit incurs a great achievement in terms of area with respect to the use of TMR [10]

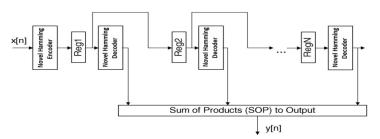

FIGURE 3: FIR filter protection with a single encoder

USER © 2013 http://www.ijser.org

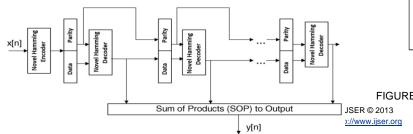

FIGURE 4 : FIR filter protection with additional data protection

# 3. IMPLEMENTATION OF PROPOSED TECHNIQUE

In this section, the proposed technique is used to demonstrate, how the lot of overhead due to interspersing the redundancy bits, their subsequent removal, pad to pad delay in the decoder and consumption of total area of FIR filter for higher bits are reduced. These are based on the novel hamming code implementation in the FIR filter instead of conventional hamming code used to protect FIR filter previously[10].

#### A . Novel Hamming Single Encoder

FIGURE 5: FIR filter protection with a single Novel encoder

One of the improvisation would be to replace the Hamming encoders and Hamming decoder[10] with Novel Hamming encoder and Novel Hamming decoder respectively, in Fig. 3. The delay in the Novel Hamming decoder reduced in comparison of conventional Hamming decoder, they are only used if there are errors in the circuit and even in that case, if only a single error is present in the register, it can still be corrected with the Novel decoder at each stage. In summary, these additional encoders are useful only if we assume that a tap value will be hit by more than one SEU at different time instants, as it propagates through the delay line

#### B. Novel Additional Hamming Data Protection

#### FIGURE 6 : FIR filter protection with Novel additional data protection

The operation observed in the above design (fig. 5) is improved in this section by using a novel addition Hamming data protection. Here , the output of each decoder is fed to the data bits of the next register while the parity bits are taken directly from the previous stage, as shown in Figure 6. This would allow recovering from multiple errors that occur in the data bits as long as they happen in different clock cycles. This is achieved without additional encoders.

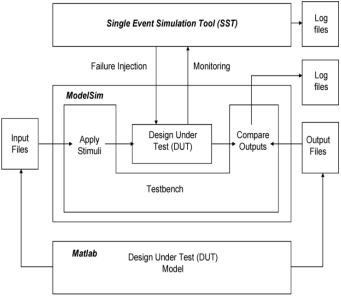

## 4. EXPERIMENTAL RESULTS

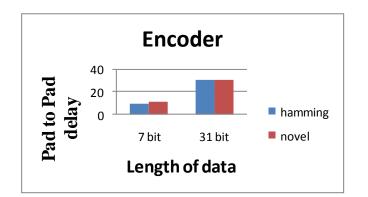

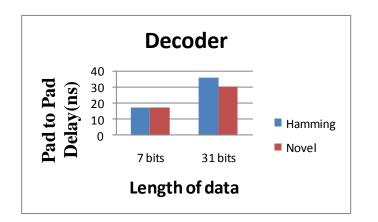

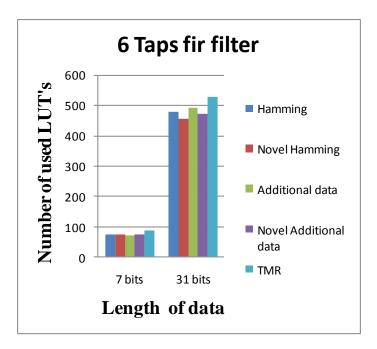

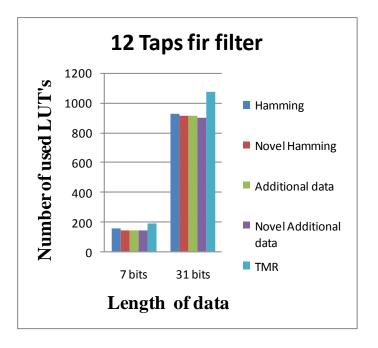

The proposed techniques have been implemented in VHDL (Xilinx 9.2) and then the circuits have been synthesized for FPGA VIRTEX-6.. An experimental setup [11] based on the Single Event Upset Simulation Tool (SST) has been used to insert SEUs, the block diagram for which is shown in figure 7. The results obtained are summarized in figure 8,9,10,11 The results clearly indicates the efficiency of the proposed techniques in terms of circuit complexity and area as compared to the traditional approaches[10].

The generic FIR filters have been implemented with 6 and 12 taps using the same structure and coefficient as in [10]. Equations (2) and (3) show the FIR filter coefficients, as mentioned in the references above.

| $h[n] = [-1\ 24\ 50\ 50\ 24\ -1]$                           | (2) |

|-------------------------------------------------------------|-----|

| <i>h</i> [ <i>n</i> ] = [1 -1 -9 6 73 120 120 73 6 -9 -1 1] | (3) |

FIGURE 8 : Comparison of Encoders in terms of delay

FIGURE 9 : Comparison of Decoders in terms of delay

Table 4 : FPGA Synthesis results for 7 and 31 bits

|         | FPGA - VERTEX 6                             | F     | IR FILTER 6 TA | Ps                                         | FIR FILTER 12 TAPs |     |     |  |

|---------|---------------------------------------------|-------|----------------|--------------------------------------------|--------------------|-----|-----|--|

|         |                                             | SLICE | FF             | LUT                                        | SLICE              | FF  | LUT |  |

|         | HAMMING WITH SINGLE ENCODER                 | 42    | 66             | 73                                         | 69                 | 132 | 153 |  |

| 7 BITS  | HAMMING ADDITION DATA<br>PROTECTION         | 27    | 66             | 70                                         | 61                 | 125 | 139 |  |

|         | NOVEL HAMMING WITH SINGLE<br>Encoder        | 27    | 66             | 72                                         | 71                 | 132 | 142 |  |

|         | NOVEL HAMMING ADDITIONAL DATA<br>Protection | 31    | 66             | 66 70 61 125   66 72 71 132   66 73 61 125 | 140                |     |     |  |

|         | HAMMING WITH SINGLE ENCODER                 | 215   | 254            | 479                                        | 385                | 476 | 922 |  |

| 24.0072 | HAMMING ADDITION DATA<br>PROTECTION         | 147   | 254            | 491                                        | 293                | 445 | 914 |  |

| 31 BITS | NOVEL HAMMING WITH SINGLE<br>Encoder        | 210   | 254            | 454                                        | 348                | 476 | 911 |  |

|         | NOVEL HAMMING ADDITIONAL DATA<br>Protection | 141   | 254            | 471                                        | 266                | 445 | 901 |  |

The VIRTEX-6 results shows The decrement in the usage of LUTs when comparing the proposed technique to the ordinary [10] as we increase the no. of bits

FIGURE 10 : Number of LUTs used in different data protection technique for 6 taps FIR Filter

FIGURE 11 : Number of LUTs used in different data protection tech-

IJSER © 2013 http://www.ijser.org nique for 12 taps FIR Filter

## 5. CONCLUSIONS

In the proposed improvement the redundancy bits are appended at the end of data bits. This eliminates the overhead of interspersing the redundancy bits at the sender end and their removal at the receiver end after checking for single-bit error and consequent correction, if any. Further the effort needed in identifying the values of the redundancy bits is lower in the proposed novel method. Hamming code is normally used for transmission of 7-bit data item. Scaling it for larger data lengths results in a lot of overhead due to interspersing the redundancy bits and their removal later. In contrast, the proposed method is highly scalable without such overhead. We see that there is only 7 bit overhead for a 56-bit data stream, which is much less compared to 4 bit overhead for a 7-bit data. A new approach for protecting the FIR filters from single event upsets (SEUs) are implemented in the design. We have focused on achieving low complexity and low area occupancy with minimum delay. Improved method can be scaled easily for larger data lengths as compared to [10]. The simulation results of the proposed designs are encouraging in terms of delay and area used. The implementation results show that the proposed design is suitable to protect FIR filters efficiently from single event upsets. Future work includes the consideration of power consumption as a metric for optimization, since it is a key factor in space applications.

# 6. REFERENCES

[1] R. D. Schrimpf and D. M. Fleetwood, 2004, Radiation Effects and Soft Errors in Integrated Circuits and Electronic Devices. Singapore:World Scientific, 981-238-940-7.

[2] P. E. DODD AND L. L. M ASSENGILL, JUN. 2003, "BASIC MECHANISMS AND MODELLING OF SINGLE-EVENT UPSET IN DIGITAL MICROELECTRON-ICS," IEEE TRANS. NUCL. SCI., VOL. 50, NO. 3, PP. 583–602

[3] P. E. DODD AND L. L. M ASSENGILL, JUN. 2003, "BASIC MECHA-NISMS AND MODELING OF SINGLE-EVENT UPSET IN DIGITAL MICROELEC-TRONICS," IEEE TRANS. NUCL. SCI., VOL. 50, NO. 3, PP. 583–602

[4] M. P. Baze, S. P. Buchner, and D. M cmorrow, Dec. 2000, "A digital CM OS technique for SEU hardening," IEEE Trans. Nucl. Sci., vol. 47, no. 6, pp.2603–2608

[5] S.M. Parkes, "DSP (Demanding Space-based Processing!): the Path Behind and the Road Ahead", 6th International Workshop on Digital Signal Processing Techniques for Space Applications, Noordwijk, The Netherlands, September 1998

[6] W. W. Peterson and E. J. Weldon, Jr., Error-Correcting Codes (2nd ed.). Cambridge, MA: MIT Press, 1972

[7] T. Fujiwara et al., "Error Detecting Capabilities of the Shortened Hamming Codes Adopted for Error Detection in IEEE Standard 802.3," IEEE Trans. Communications, vol. 37, no. 9, pp. 986–989, Sep 1989.

[8] W. Xiong, and D. W. Matolak, "Performance of Hamming Codes in Systems Employing Different Code Symbol Energies," IEEE Communications Society, pp. 1055–1058 [Wireless and Communications and Networking Conference (WCNC)].

[9] B. Shim, N.R Shanbhag and S. Lee, "Energy-efficient soft error-

tolerant digital signal processing", Signals, Systems and Computers Conference Record of the Thirty-Seventh Asilomar, 2003, pp. 1493 - 1497.

[10] Shih-Fu Liu, Pedro Reviriego and Juan Antonio Maestro, "Fault Tolerant FIR Filters Using Hamming Codes", RADECS 2009 Proceedings

[11] O. Ruano, J.A. Maestro, P. Reviriego, "Performance Analysis and Improvements for a Simulation-based Fault Injection Platform", Proc. of IEEE International Symposium on Industrial Electronics (ISIE'08), Cambridge (U.K.), June 2008, pp. 2299-2304.

## 7. AUTHOPRS PROFILE

**1. Associate Prof. Rashmi Sinha :** Department of Electronics and Communication Engineering , National Institute of technology, Jamshedpur (India)

Email : rsinha.ece@nitjsr.ac.in

**2. Brajesh Kumar Gupta :** M.Tech Scholar , Department of Electronics and Communication Engineering , National Institute of technology, Jamshedpur (India)

Email : <u>bkgupta8bu@gmail.com</u>